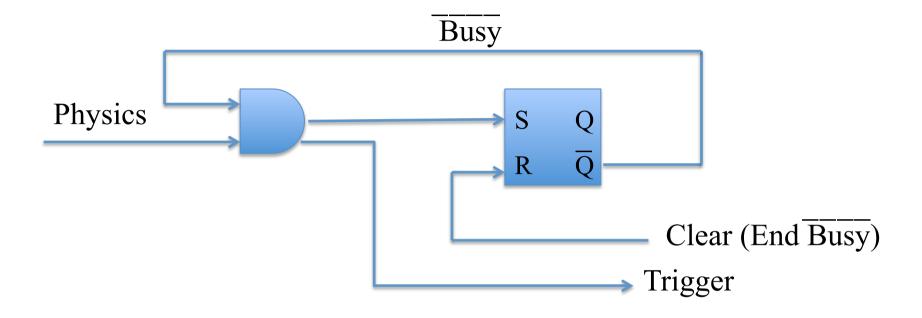

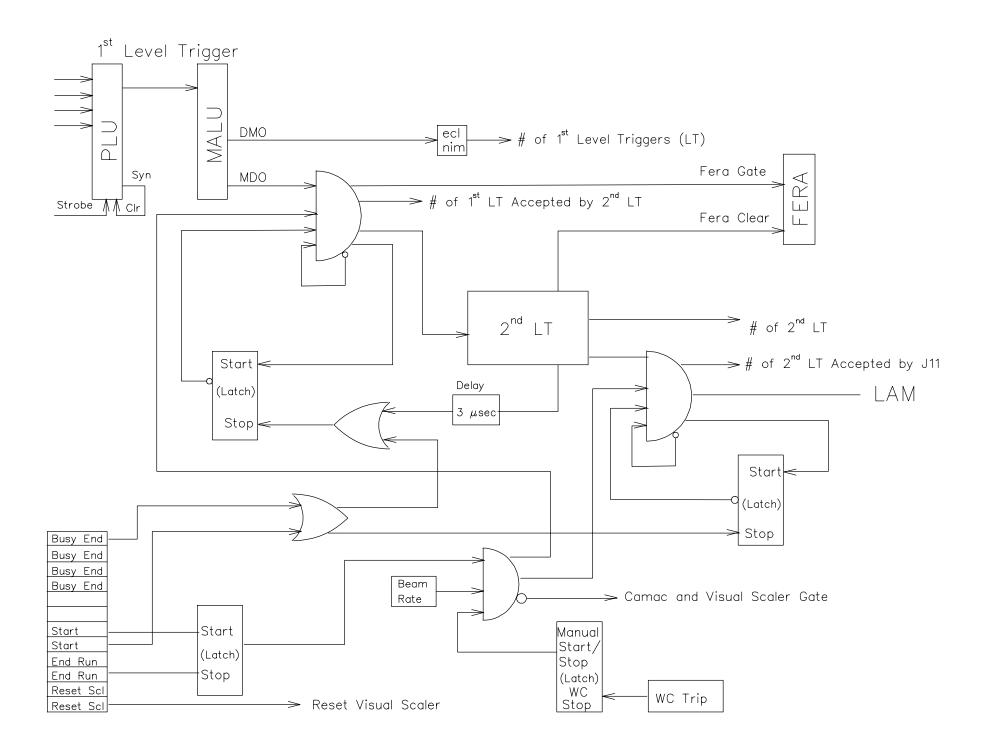

The arrival of a "Physics" event will generate a "Trigger" signal which is sent to the computer. At the same time the Trigger will inhibit the coincidence to future events by setting the "Busy-bar" signal (which will go to "zero"). The coincidence will remain inhibited until a Clear signal is sent by the computer which will end the Busy-bar signal and open the coincidence to future Physics events.

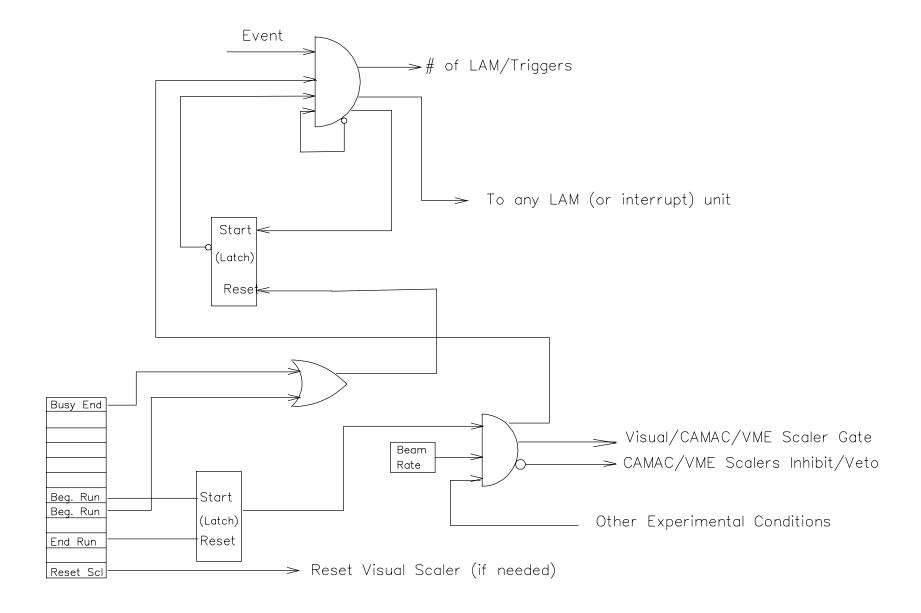

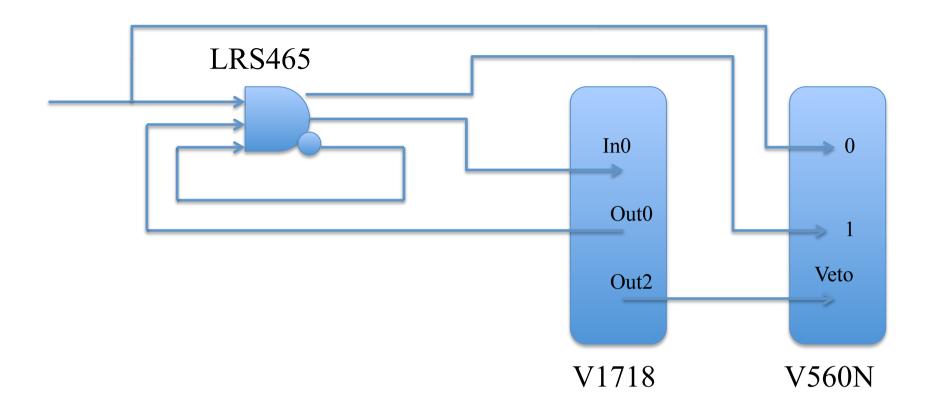

Out0 = Busy-bar : Start via SW at Begin Run

Reset via In0 at "Physics"

Start via SW at End of Read Cycle

Out2 = Veto : Start via SW at Begin Run [Inv.Pol.]

Stop via SW at End of Run

Out0 and Out2 are levels, since width > period

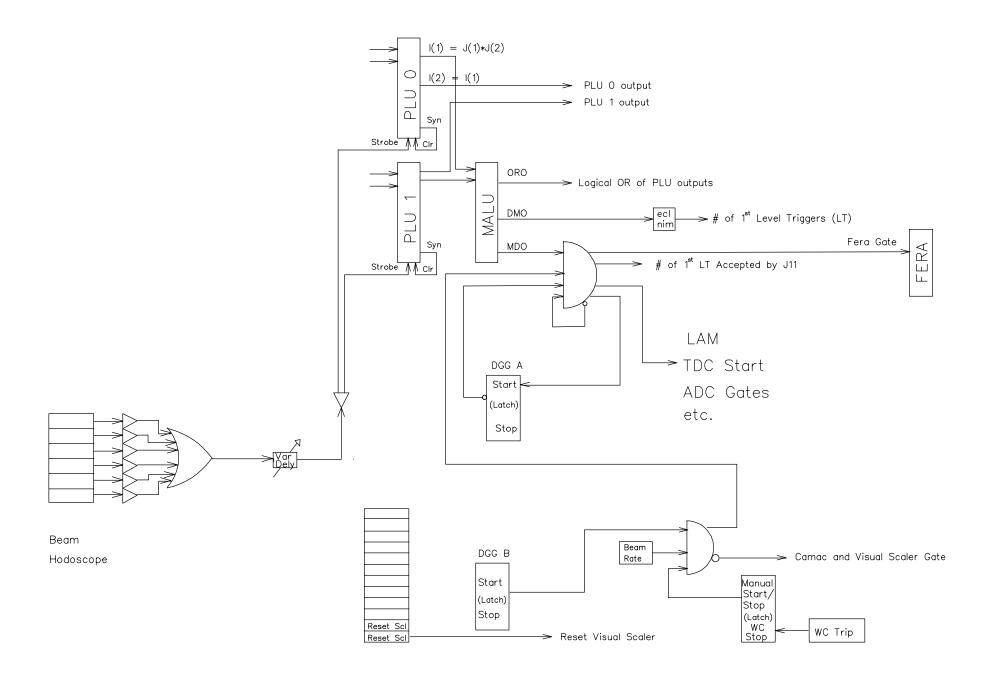

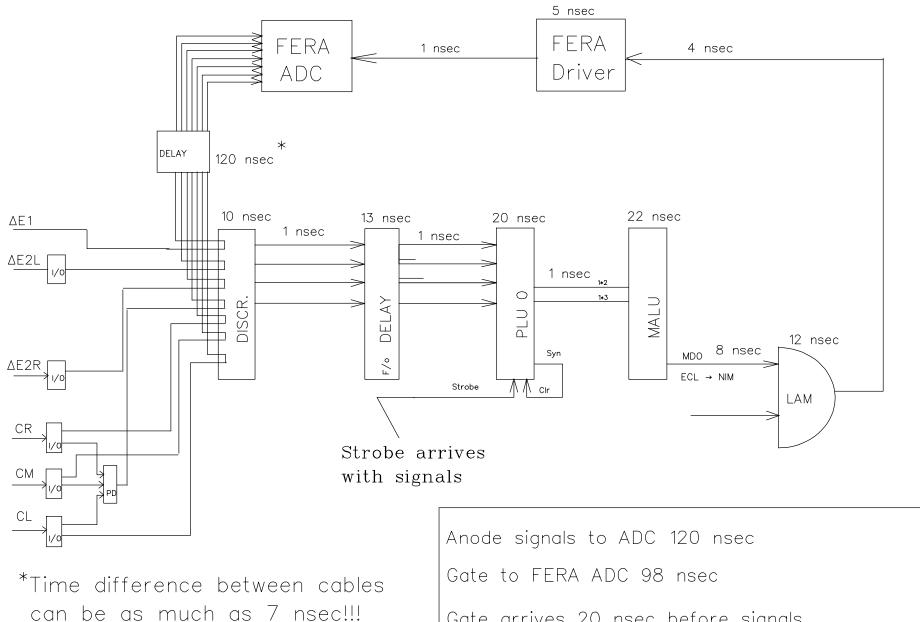

Table of Delay times

Gate arrives 20 nsec before signals

N.B. Times O is entrance to Discriminator

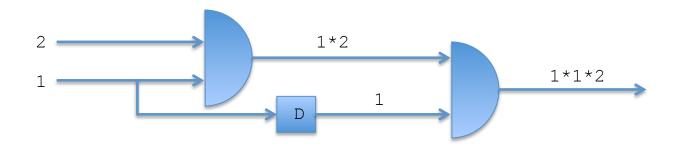

## Coincidence between physics signal and external clock (Prescaling)

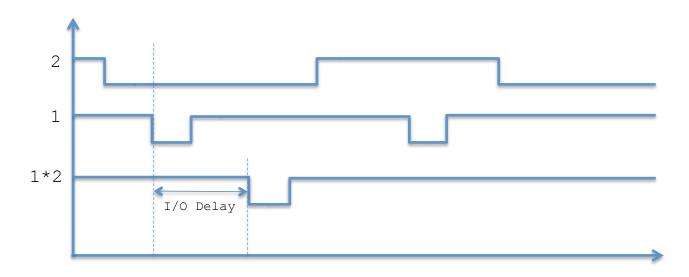

"1" is the physics signal and "2" is a clock used for for Prescaling (i.e. reducing) the number of events.

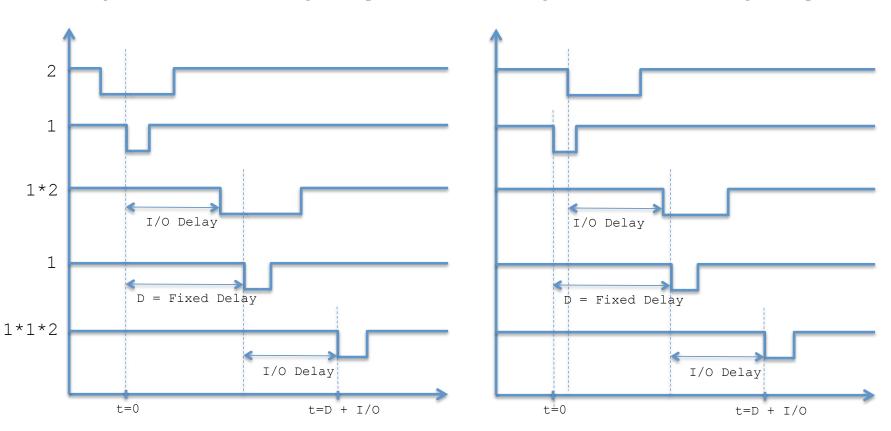

PROBLEM: If the leading edge of "2" arrives after that of "1" then we have the time of the coincidence given by the clock and NOT by the physics signal. The solution to this is to build a proper coincidence circuit (next page). Let's assume that the Input-Output delay of the instrument to be "I/O". Then by making a proper choice of the fixed delay "D" (function of "I/O" and of the width of the two signals "1" and "2") the circuit can be built in such a way that the timing is ALWAYS given by signal "1", even in those cases in which signal "2" arrives after "1". The output of the second coincidence will be delayed wrt the input of "1" by the same amount given by "I/O + D".

Timing of first coincidence given by "1"

Timing of first coincidence given by "2"